SLMLET2は、System Verilogのインタフェース機能を使っているため、必要なファイルを揃えてやらないと論理合成ができない。以下の2つの問題点がある

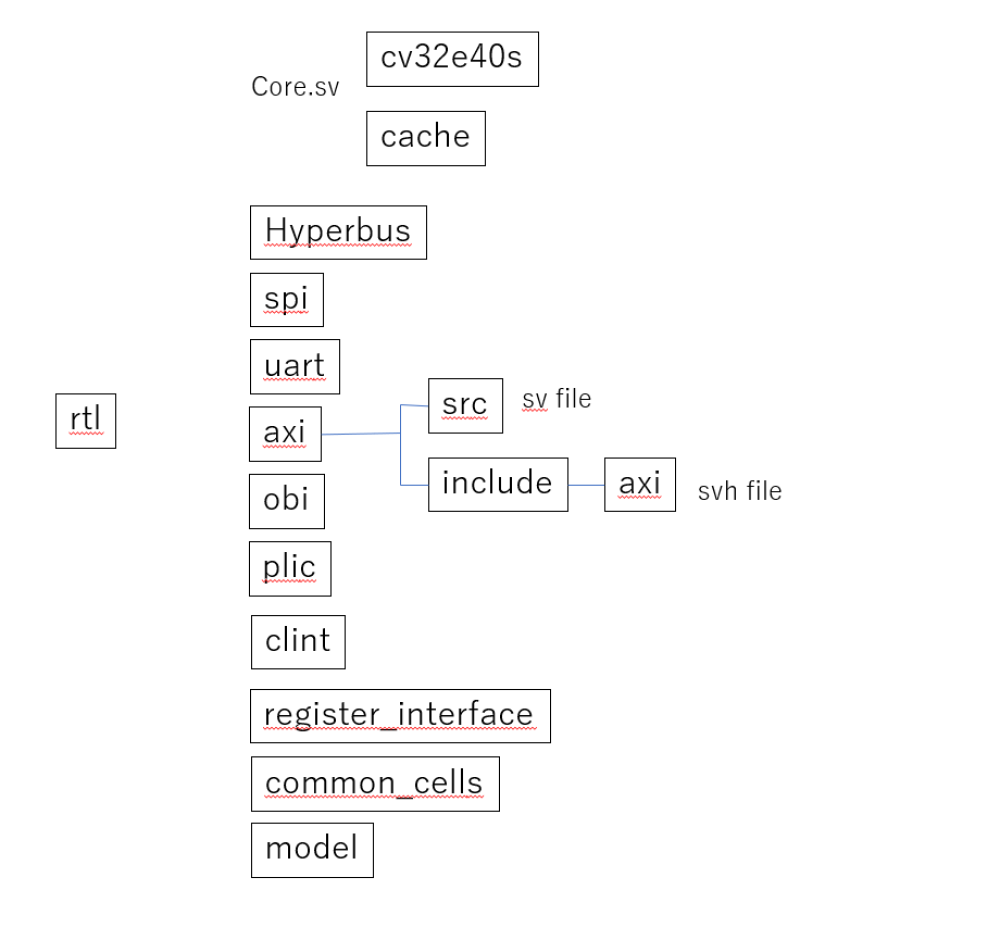

ディレクトリ構造は、割と普通で、この図のrtlと並置するsynの中に合成用のtclを置いて実行する仕様になる。

問題は、rtl内の記述がinclude文でsvh fileをincludeしているが、そのディレクトリが存在しないことと、interfaceを定義する記述はソースコード中でincludeするだけではダメで、あらかじめ定義のファイルを読み込んでおく必要がある。例えば、uartのトップファイルはaxi_uart_intfで、ここでは

`include "axi/assign.svh"

`include "axi/typedef.svh"

`include "register_interface/assign.svh"

`include "register_interface/typedef.svh"

がインクルードされているのだが、axi, register_interfaceは、このディレクトリ内に存在せず、uartディレクトリから../axi/include/axiの下にある。このディレクトリは存在しないとファイル自体の読み込みができない。そこで、パスに以下を付け加える。

lappend search_path ../rtl/axi/include

lappend search_path ../rtl/register_interface/include

includeというディレクトリ構造はこれを意識して作られているのだと考えられる。

ところが、interface文で定義した記述を利用する場合、(たとえばAXI_LITE.Slave など)このAXI_LITEの定義がassign.svh中に存在しても、include文で参照するだけではエラーになってしまう。これらのファイルはあらかじめalayzeしてやる必要がある。これは個別指定しかないので以下のようにtclを書いてやる

analyze -format sverilog ../rtl/axi/src/axi_pkg.sv

analyze -format sverilog ../rtl/axi/src/axi_intf.sv

analyze -format sverilog ../rtl/register_interface/src/reg_intf.sv

analyze -format sverilog $rtl_dir/axi/assign.svh

analyze -format sverilog $rtl_dir/axi_uart.sv

analyze -format sverilog $rtl_dir/BaudRateGen.v

analyze -format sverilog $rtl_dir/CSR.v

analyze -format sverilog $rtl_dir/Receiver.v

analyze -format sverilog $rtl_dir/SimpleSCI.v

analyze -format sverilog $rtl_dir/Transmitter.v

analyze -format sverilog $rtl_dir/uart_fifo.sv

elaborate $base_name

current_design $base_name

link

uniquify

結論として、interface文の定義は、当該ファイルをanalyzeし、それ以外はpathにincludeディレクトリを加えてやることで合成が可能である。