Libero SoCのアイコンをクリックしてツールを上げる

Project→New Project

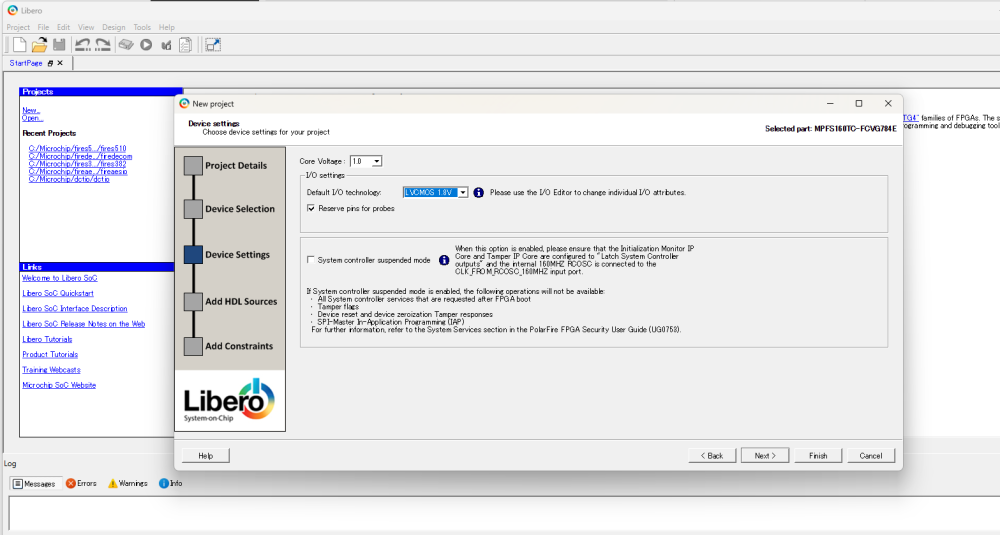

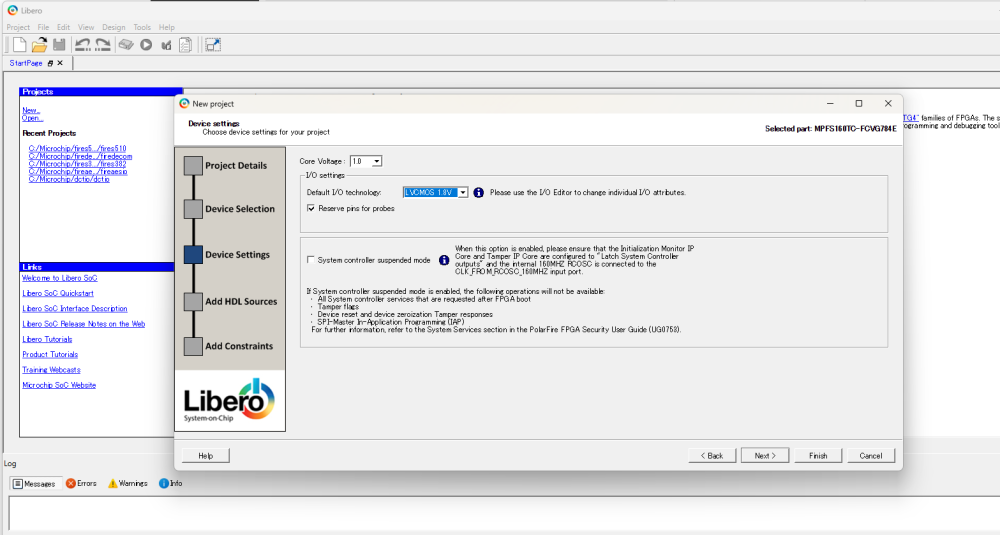

Wizardに沿って名前を決めて入力 HDL fileとConstraints fileをImport、Constraints fileは普通sdcを使うので、ファイルの種類を切り替えて(デフォルトがpdcになっている)Importする

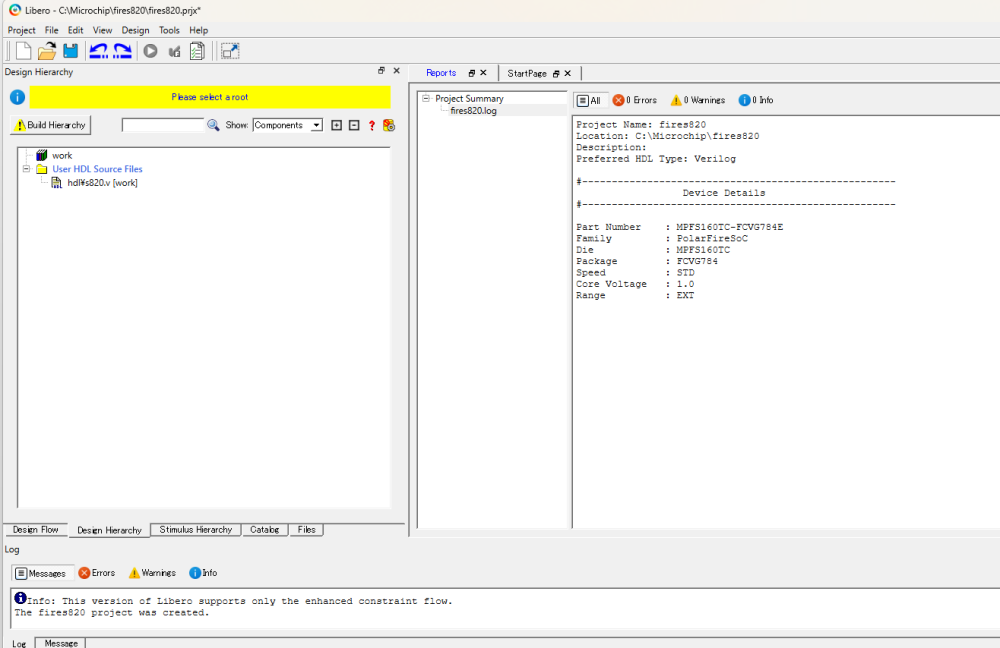

左のWindowsの切り替えメニューが下の方についているので、これをDesign Hierarchyにする

左上のBuild Hierarchyというボタンをクリック、workの下にImportしたVerilogのモジュール名が出てくるので、これをマウスの右ボタンでクリックし、メニューの中のSet Root nodeを選択。上に出ている黄色のPlease select rootのワーニングが消えるのを確認する

下の切り替えメニューをDesgin Flowに戻し、今度はConstraintsを選択、Manage Constraintsをクリックし、上の方のメニューでTimingを選択すると、最初にImportしたsdcファイルが出てくる。このボタンにすべてチェックを入れて、Saveする。これを忘れると読み込んでも使われない

Place and Routeをダブルクリックすると、Symplify Liteを使ってSynthesisした後に、Place and Routeしてくれる(この辺の雰囲気もLibero IDTとはかなり違う)

Errorなく終了したら、Verify Timing、Open Smart Timing、Open Smart Powerを順にクリックすると、クリティカルパス、最大動作周波数、電力見積もりが出てくる

ここから先のプログラミングはやったことがない。。。